Nathan, A., Saha, S.K. & Todi, R. M. (eds) 75th Anniversary of the Transistor (Wiley-IEEE, 2023).

Borkar, S. & Chien, A. A. The future of microprocessors. Commun. ACM 54, 67–77 (2011).

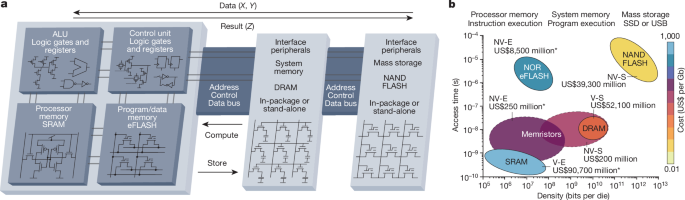

Sebastian, A., Le Gallo, M., Khaddam-Aljameh, R. & Eleftheriou, E. Memory devices and applications for in-memory computing. Nat. Nanotechnol. 15, 529–544 (2020).

Yole Intelligence. Emerging Non-volatile Memory 2024 (Market Analysis Report). Report No. YINTR24412. https://www.yolegroup.com/product/report/emerging-non-volatile-memory-2024/ (Yole Group, 2024).

Intel Corporation. The story of the Intel® 4004. https://www.intel.com/content/www/us/en/history/museum-story-of-intel-4004.html (Accessed 24 March 2025).

Amirsoleimani, A. et al. In-memory vector-matrix multiplication in monolithic complementary metal–oxide–semiconductor-memristor integrated circuits: design choices, challenges, and perspectives. Adv. Intell. Syst. 2, 2000115 (2020).

Backus, J. Can programming be liberated from the von Neumann style? A functional style and its algebra of programs. Commun. ACM 21, 613–641 (1978).

Horowitz, M. 1.1 Computing’s energy problem (and what we can do about it). In Proc. 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC) 10–14 (IEEE, 2014).

Keckler, S. W., Dally, W. J., Khailany, B., Garland, M. & Glasco, D. GPUs and the future of parallel computing. IEEE Micro 31, 7–17 (2011).

Zhang, C. et al. iMLBench: a machine learning benchmark suite for CPU-GPU integrated architectures. IEEE Trans. Parallel Distrib. Syst. 32, 1740–1752 (2021).

Li, F., Ye, Y., Tian, Z. & Zhang, X. CPU versus GPU: which can perform matrix computation faster—performance comparison for basic linear algebra subprograms. Neural Comput. Appl. 31, 4353–4365 (2019).

NVIDIA. NVIDIA H100 Tensor Core GPU. Datasheet https://resources.nvidia.com/en-us-tensor-core/nvidia-tensor-core-gpu-datasheet (NVIDIA, 2024).

Rattani, A., Reddy, N. & Derakhshani, R. Multi-biometric convolutional neural networks for mobile user authentication. In Proc. 2018 IEEE International Symposium on Technologies for Homeland Security (HST) 1–6 (IEEE, 2018).

BBVA. Biometrics and machine learning: the accurate, secure way to access your bank. News BBVA. https://www.bbva.com/en/biometrics-and-machine-learning-the-accurate-secure-way-to-access-your-bank/ (2020).

Ingle, P. Y. & Kim, Y.-G. Real-time abnormal object detection for video surveillance in smart cities. Sensors 22, 3862 (2022).

Amerini, I., Li, C.-T. & Caldelli, R. Social network identification through image classification with CNN. IEEE Access 7, 35264–35273 (2019).

Tan, X., Qin, T., Soong, F. & Liu, T.-Y. A Survey on Neural Speech Synthesis. Preprint at arxiv.org/abs/2106.15561 (2021).

Introducing ChatGPT. Open AI. https://openai.com/blog/chatgpt (Accessed 24 March 2025).

Hong, T., Choi, J.-A., Lim, K. & Kim, P. Enhancing personalized ads using interest category classification of SNS users based on deep neural networks. Sensors 21, 199 (2021).

European Commission. EU action plan on digitalising the energy system. European Commission https://ec.europa.eu/commission/presscorner/detail/en/qanda_22_6229 (2022).

Jones, N. How to stop data centres from gobbling up the world’s electricity. Nature 561, 163–166 (2018).

Microsoft. 2022 Environmental sustainability report. Microsoft https://www.microsoft.com/en-us/corporate-responsibility/sustainability/report (2022).

Crawford, K. Generative AI’s environmental costs are soaring – and mostly secret. Nature 626, 693–693 (2024).

Aguirre, F. et al. Hardware implementation of memristor-based artificial neural networks. Nat. Commun. 15, 1974 (2024).

Jhang, C.-J., Xue, C.-X., Hung, J.-M., Chang, F.-C. & Chang, M.-F. Challenges and trends of SRAM-based computing-in-memory for AI edge devices. IEEE Trans. Circuits Syst. I 68, 1773–1786 (2021).

Zhang, Y. et al. A 40nm 1Mb 35.6 TOPS/W MLC NOR-Flash based computation-in-memory structure for machine learning. In Proc. 2021 IEEE International Symposium on Circuits and Systems (ISCAS) 1–5 (IEEE, 2021).

Shi, T. et al. Stochastic neuro-fuzzy system implemented in memristor crossbar arrays. Sci. Adv. 10, eadl3135 (2024).

Lanza, M. et al. Memristive technologies for data storage, computation, encryption, and radio-frequency communication. Science 376, eabj9979 (2022).

Yang, J. J., Strukov, D. B. & Stewart, D. R. Memristive devices for computing. Nat. Nanotechnol. 8, 13–24 (2013).

Mehonic, A. et al. Roadmap to neuromorphic computing with emerging technologies. APL Mater. 12, 109201 (2024).

Torrezan, A. C., Strachan, J. P., Medeiros-Ribeiro, G. & Williams, R. S. Sub-nanosecond switching of a tantalum oxide memristor. Nanotechnology 22, 485203 (2011).

Tan, C. L. Comparison: latest 3D NAND products from YMTC, Samsung, SK hynix and Micron. Tech Insights https://www.techinsights.com/blog/comparison-latest-3d-nand-products-ymtc-samsung-sk-hynix-and-micron (2023).

SK hynix begins mass production of industry’s highest 238-layer 4D NAND. SK hynix https://news.skhynix.com/sk-hynix-begins-mass-production-of-industrys-highest-238-layer-4d-nand/ (2023).

Heyman, K. Is there a limit to the number of layers in 3D-NAND? Semiconductor Engineering https://semiengineering.com/is-there-a-limit-to-the-number-of-layers-in-3d-nand/ (2022).

Belmonte, A. et al. Capacitor-less, Long-Retention (>400s) DRAM cell paving the way towards low-power and high-density monolithic 3D DRAM. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM) 28.2.1–28.2.4 (IEEE, 2020).

Han, J. W. et al. Ongoing evolution of DRAM scaling via third dimension -vertically stacked DRAM -. In Proc. 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023).

Yu, S. & Kim, T.-H. Semiconductor memory technologies: state-of-the-art and future trends. Computer 57, 150–154 (2024).

Tsuda, S. et al. First demonstration of FinFET split-gate MONOS for high-speed and highly-reliable embedded Flash in 16/14nm-node and beyond. In Proc. 2016 IEEE International Electron Devices Meeting (IEDM) 11.1.1–11.1.4 (IEEE, 2016).

LaPedus, M. Embedded Flash scaling limits (Semiconductor Engineering, 2018).

Ramkumar, K. et al. A scalable, low voltage, low cost SONOS memory technology for embedded NVM applications. In Proc. 2013 5th IEEE International Memory Workshop 199–202 (2013).

Mehonic, A. & Kenyon, A. J. Brain-inspired computing needs a master plan. Nature 604, 255–260 (2022).

Franca, D. GPT4—all details leaked. Medium https://medium.com/@daniellefranca96/gpt4-all-details-leaked-48fa20f9a4a (2023).

ChatGPT’s carbon footprint. karmametrix.com https://karmametrix.com/blog/web-sustainability/the-carbon-footprint-of-chatgpt/ (2023).

Kim, S. AI landscape is shifting from GPU to AI Accelerator. Medium https://sungkim11.medium.com/ai-landscape-is-shifting-from-gpu-to-ai-accelerator-5dc1aeaffdc (2023).

Google. GPU pricing. Google https://cloud.google.com/compute/gpus-pricing (2025)

Gwennap, L. Expedera redefines AI acceleration for the edge. Expedera https://www.expedera.com/expedera-redefines-ai-acceleration-for-the-edge/ (2021).

Barnell, M., Raymond, C., Wilson, M., Isereau, D. & Cicotta, C. Target classification in synthetic aperture radar and optical imagery using Loihi neuromorphic hardware. In Proc. 2020 IEEE High Performance Extreme Computing Conference (HPEC) 1–6 (https://ieeexplore.ieee.org/document/9286246; IEEE, 2020).

Viale, A., Marchisio, A., Martina, M., Masera, G. & Shafique, M. CarSNN: an efficient spiking neural network for event-based autonomous cars on the Loihi neuromorphic research processor. In Proc. 2021 International Joint Conference on Neural Networks (IJCNN) 1–10 (IEEE, 2021).

Orchard, G. et al. Efficient neuromorphic signal processing with Loihi 2. In Proc. 2021 IEEE Workshop on Signal Processing Systems (SiPS) 254–259 (IEEE, 2021).

Analog Devices. MAX78002 datasheet and product information. Analog Devices https://www.analog.com/en/products/max78002.html (2022).

Eleftheriou, E. The Metis AI platform: a technical deepdive. Axelera Artificial Intelligence https://www.axelera.ai/blog/the-metis-ai-platform-in-detail (2023).

Mythic AI. Taking powerful, efficient inference to the edge. Mythic AI https://mythic.ai/wp-content/uploads/2022/02/MythicWhitepaper-2019oct31.pdf (2019).

Moore, S. K. Two startups use processing in Flash memory for AI at the edge. IEEE Spectrum. https://spectrum.ieee.org/two-startups-use-processing-in-flash-memory-for-ai-at-the-edge (2018).

Mythic. M1076 analog matrix processor. Mythic https://mythic.ai/products/m1076-analog-matrix-processor/ (Accessed 18 April 2024).

Sinangil, M. E. et al. A 7-nm compute-in-memory SRAM macro supporting multi-bit input, weight and output and achieving 351 TOPS/W and 372.4 GOPS. IEEE J. Solid-State Circuits 56, 188–198 (2021).

Fujiwara, H. et al. 34.4 A 3nm, 32.5TOPS/W, 55.0TOPS/mm2 and 3.78Mb/mm2 fully-digital compute-in-memory macro supporting INT12 × INT12 with a parallel-MAC architecture and foundry 6T-SRAM bit cell. In Proc. 2024 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67, 572–574 (IEEE, 2024).

Infineon Technologies. Embedded Flash IP solutions. Infineon Technologies https://www.infineon.com/cms/en/product/memories/embedded-flash-ip-solutions/ (2025).

Xie, S. et al. 16.2 eDRAM-CIM: compute-In-memory design with reconfigurable embedded-dynamic-memory array realizing adaptive data converters and charge-domain computing. In Proc. 2021 IEEE International Solid-State Circuits Conference (ISSCC), Vol. 64, 248–250 (IEEE, 2021).

Khakifirooz, A. et al. A 1.67Tb, 5b/cell Flash memory fabricated in 192-layer floating gate 3D-NAND technology and featuring a 23.3 Gb/mm2 bit density. In Proc. 2023 IEEE International Solid-State Circuits Conference (ISSCC) 27–29 https://doi.org/10.1109/ISSCC42615.2023.10067616 (IEEE, 2023).

Kim, M., Liu, M., Everson, L. R. & Kim, C. H. An embedded nand Flash-based compute-in-memory array demonstrated in a standard logic process. IEEE J. Solid-State Circuits 57, 625–638 (2022).

Merrikh-Bayat, F. et al. High-performance mixed-signal neurocomputing with nanoscale floating-gate memory cell arrays. IEEE Trans. Neural Netw. Learn. Syst. 29, 4782–4790 (2018).

Hu, H.-W. et al. A 512Gb in-memory-computing 3D-NAND Flash supporting similar-vector-matching operations on edge-AI devices. In Proc. 2022 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 65, 138–140 (IEEE, 2022).

Hsu, P.-K., Garg, V., Lu, A. & Yu, S. A heterogeneous platform for 3D NAND-based in-memory hyperdimensional computing engine for genome sequencing applications. IEEE Trans. Circuits Syst. I 71, 1628–1637 (2024).

Pearson, A. D., Northover, W., Dewald, J. F. & Peck, W. Jr Chemical, physical, and electrical properties of some unusual inorganic glasses. Adv. Glass Technol. 2, 357–365 (1962).

Yang, J. J. et al. Memristive switching mechanism for metal/oxide/metal nanodevices. Nat. Nanotechnol. 3, 429–433 (2008).

Tsuji, K. et al. 0.1 \mum-rule MRAM development using double-layered hard mask. In International Electron Devices Meeting. Technical Digest (Cat. No. 01CH37224) 36.4.1–36.4.4 (IEEE, 2001).

Oh, S.-H. et al. Noble FeRAM technologies with MTP cell structure and BLT ferroelectric capacitors. In Proc. IEEE International Electron Devices Meeting 2003 34.5.1–34.5.4 (IEEE, 2003).

Intel Corporation. Intel and Micron produce breakthrough memory technology. Intel Corporation https://www.intc.com/news-events/press-releases/detail/324/intel-and-micron-produce-breakthrough-memory-technology (2015).

Panasonic Newsroom Global. Panasonic starts world’s first mass production of ReRAM mounted microcomputers. Panasonic Newsroom Global https://news.panasonic.com/global/press/en130730-2 (2013).

EE Times. MRAM debut cues memory transition. EE Times https://www.eetimes.com/MRAM-debut-cues-memory-transition/ (2006).

Arnaud, F. et al. High density embedded PCM cell in 28nm FDSOI technology for automotive micro-controller applications. In Proc. 2020 IEEE International Electron Devices Meeting (IEDM) 24.2.1–24.2.4 (IEEE, 2020).

Chou, C.-C. et al. An N40 256K×44 embedded RRAM macro with SL-precharge SA and low-voltage current limiter to improve read and write performance. In Proc. 2018 IEEE International Solid-State Circuits Conference (ISSCC) 478–480 (2018).

Lin, K.-F. et al. 15.9 A 16nm 16Mb embedded STT-MRAM with a 20ns write time, a 1012 write endurance and integrated margin-expansion schemes. In 2024 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67, 292–294 (IEEE, 2024).

Lanza, M., Molas, G. & Naveh, I. The gap between academia and industry in resistive switching research. Nat. Electron. 6, 260–263 (2023).

Rao, S. et al. Spin-orbit torque MRAM for ultrafast cache and neuromorphic computing applications. In Proc. 2023 IEEE International Memory Workshop (IMW) 1–4 (IEEE, 2023).

Gupta, M. et al. Ultimate MRAM scaling: design exploration of high-density, high-performance and energy-efficient VGSOT for last level cache. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Intel Corporation. Intel reports second-quarter 2022 financial results. Intel Corporation https://www.intc.com/news-events/press-releases/detail/1563/intel-reports-second-quarter-2022-financial-results (2022).

Fujitsu. Introducing ReRAM. Fujitsu https://www.fujitsu.com/jp/group/fsm/en/products/reram/ (Accessed 24 March 2025).

Infineon Technologies. PSOC™ Edge – next generation of ML enabled MCUs. Infineon Technologies https://www.infineon.com/cms/en/product/promopages/next-generation-mcu/ (Accessed 24 March 2025).

Everspin Technologies. Utilizing Everspin STT-MRAM in enterprise SSDs to simplify power-fail protection and increase density, performance, and endurance. Everspin Technologies https://www.everspin.com/file/156345/download (2018).

Huang, Y.-C. et al. 15.7 A 32Mb RRAM in a 12nm FinFet technology with a 0.0249μm2 bit-cell, a 3.2GB/S read throughput, a 10KCycle write endurance and a 10-year retention at 105 °C. In 2024 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 67, 288–290 (IEEE, 2024).

Xue, C.-X. et al. 15.4 A 22nm 2Mb ReRAM compute-in-memory macro with 121-28TOPS/W for multibit MAC computing for tiny AI edge devices. In 2020 IEEE International Solid-State Circuits Conference (ISSCC) 244–246 (IEEE, 2020).

GlobalFoundries. GlobalFoundries acquires Renesas’ non-volatile resistive RAM technology to proliferate IoT and 5G applications. https://gf.com/gf-press-release/globalfoundries-acquires-renesas-non-volatile-resistive-ram-technology-toproliferate-iot-and-5g-applications/ (2023).

Weebit. Weebit Nano to demo its ReRAM technology on GlobalFoundries’ 22FDX® platform. https://www.weebitnano.com/news/press-releases/weebit-nano-to-demo-its-reram-rram-embedded-technology-on-globalfoundries-22fdxplatform/ (2024).

Lee, K. et al. 22-nm FD-SOI embedded MRAM with full solder reflow compatibility and enhanced magnetic immunity. In 2018 IEEE Symposium on VLSI Technology 183–184 (IEEE, 2018).

Lee, T. Y. et al. World-most energy-efficient MRAM technology for non-volatile RAM applications. In Proc. 2022 International Electron Devices Meeting (IEDM) 10.7.1–10.7.4 (IEEE, 2022).

Kang, G. et al. A 14nm 128Mb eMRAM implemented with 17.88Mb/mm2 at 0.60V for Auto-G1 applications. In Proc. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024).

Samsung Newsroom. Samsung Electronics unveils automotive process strategy at Samsung Foundry Forum 2023 EU. Samsung Newsroom https://news.samsung.com/global/samsung-electronics-unveils-automotive-process-strategy-at-samsung-foundry-forum-2023-eu (2023).

Marini, B. Weebit Nano’s ReRAM IP Weebit Nano’s ReRAM IP achieves high temperature qualification in SkyWater Technology’s S130 process. Skywater Technology https://www.skywatertechnology.com/weebit-nano-reram-ip-achieves-high-temperature-qualification-in-skywater-s130-process/ (2023).

Khaddam-Aljameh, R. et al. HERMES-Core—a 1.59-TOPS/mm2 PCM on 14-nm CMOS in-memory compute core using 300-ps/LSB linearized CCO-based ADCs. IEEE J. Solid-State Circuits 57, 1027–1038 (2022).

Le Gallo, M. et al. A 64-core mixed-signal in-memory compute chip based on phase-change memory for deep neural network inference. Nat. Electron. 6, 680–693 (2023).

Song, W. et al. Programming memristor arrays with arbitrarily high precision for analog computing. Science 383, 903–910 (2024).

Rao, M. et al. Thousands of conductance levels in memristors integrated on CMOS. Nature 615, 823–829 (2023).

Hu, M. et al. Memristor-based analog computation and neural network classification with a dot product engine. Adv. Mater. 30, 1705914 (2018).

Yao, P. et al. Fully hardware-implemented memristor convolutional neural network. Nature 577, 641–646 (2020).

Joshi, V. et al. Accurate deep neural network inference using computational phase-change memory. Nat. Commun. 11, 2473 (2020).

Cai, F. et al. A fully integrated reprogrammable memristor–CMOS system for efficient multiply–accumulate operations. Nat. Electron. 2, 290–299 (2019).

Chen, W.-H. et al. CMOS-integrated memristive non-volatile computing-in-memory for AI edge processors. Nat. Electron. 2, 420–428 (2019).

Zhang, W. et al. Edge learning using a fully integrated neuro-inspired memristor chip. Science 381, 1205–1211 (2023).

Deaville, P., Zhang, B. & Verma, N. A 22nm 128-kb MRAM row/column-parallel in-memory computing macro with memory-resistance boosting and multi-column ADC readout. In Proc. 2022 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 268–269 (IEEE, 2022).

Chiu, Y.-C. et al. A CMOS-integrated spintronic compute-in-memory macro for secure AI edge devices. Nat. Electron. 6, 534–543 (2023).

Wen, T.-H. et al. Fusion of memristor and digital compute-in-memory processing for energy-efficient edge computing. Science 384, 325–332 (2024).

Wan, W. et al. A compute-in-memory chip based on resistive random-access memory. Nature 608, 504–512 (2022).

Hsu, H.-H. et al. A nonvolatile AI-edge processor with SLC–MLC hybrid ReRAM compute-in-memory macro using current–voltage-hybrid readout scheme. IEEE J. Solid-State Circuits 59, 116–127 (2024).

Khwa, W.-S. et al. A 40-nm, 2M-cell, 8b-precision, hybrid SLC-MLC PCM computing-in-memory macro with 20.5 – 65.0TOPS/W for tiny-Al edge devices. In Proc. 2022 IEEE International Solid-State Circuits Conference (ISSCC) Vol. 65, 1–3 (IEEE, 2022).

Ambrogio, S. et al. An analog-AI chip for energy-efficient speech recognition and transcription. Nature 620, 768–775 (2023).

Huang, W.-H. et al. A nonvolatile Al-edge processor with 4MB SLC-MLC hybrid-mode ReRAM compute-in-memory macro and 51.4-251TOPS/W. In Proc. 2023 IEEE International Solid-State Circuits Conference (ISSCC) 15–17 (IEEE, 2023).

Jung, S. et al. A crossbar array of magnetoresistive memory devices for in-memory computing. Nature 601, 211–216 (2022).

You, D.-Q. et al. A 22nm nonvolatile AI-edge processor with 21.4TFLOPS/W using 47.25Mb lossless-compressed-computing STT-MRAM near-memory-compute macro. In Proc. 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024).

Song, M. Y. et al. High RA dual-MTJ SOT-MRAM devices for high speed (10ns) compute-in-memory applications. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Kopperberg, N. et al. Endurance of 2 Mbit based BEOL integrated ReRAM. IEEE Access 10, 122696–122705 (2022).

Wiefels, S. et al. Reliability aspects of 28 nm BEOL-integrated resistive switching random access memory. Phys. Status Solidi 221, 2300401 (2024).

Lanza, M. et al. Standards for the characterization of endurance in resistive switching devices. ACS Nano 15, 17214–17231 (2021).

SkyWater. Sky130 PDK documentation—user guide. https://sky130-fd-pr-reram.readthedocs.io/en/latest/user_guide.htmlSkyWater (Accessed 22 April 2024).

Min, D. et al. 18nm FDSOI Technology Platform embedding PCM & Innovative Continuous-Active Construct Enhancing Performance for Leading-Edge MCU Applications. In Proc. 2021 IEEE International Electron Devices Meeting (IEDM) 13.1.1–13.1.4 (IEEE, 2021).

Li, H. et al. Memristive crossbar arrays for storage and computing applications. Adv. Intell. Syst. 3, 2100017 (2021).

Ambrosi, E. et al. Low voltage (<1.8 V) and high endurance (>1M) 1-Selector/1-STT-MRAM with ultra-low (1 ppb) read disturb for high density embedded memory arrays. In Proc. 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023).

Seo, S. M. et al. First demonstration of full integration and characterization of 4F2 1S1M cells with 45 nm of pitch and 20 nm of MTJ size. In Proc. 2022 International Electron Devices Meeting (IEDM) 10.1.1–10.1.4 (IEEE, 2022).

Kim, H., Mahmoodi, M. R., Nili, H. & Strukov, D. B. 4K-memristor analog-grade passive crossbar circuit. Nat. Commun. 12, 5198 (2021).

Jeon, K. et al. Self-rectifying resistive memory in passive crossbar arrays. Nat. Commun. 12, 2968 (2021).

TSMC. Collaboration programs. TSMC https://research.tsmc.com/chinese/collaborations/academic/academic-programs.html (2025).

MXIC. Macronix, IBM and Infineon launch exploratory research initiative on phase change memory technology. MXIC https://www.mxic.com.tw/en-us/about/news/Pages/2010040392.aspx (2005).

Clarke, P. IBM, SK Hynix sign phase-change memory deal. EE Times https://www.eetimes.com/ibm-sk-hynix-sign-phase-change-memory-deal/ (2012).

NeuroSoc. An ambitious project focused on IMC. https://neurosoc.eu/ (Accessed 18 April 2024).

Muse Semiconductor. TSMC MPW shared block MPW services and price. Muse Semiconductor https://www.musesemi.com/shared-block-tapeout-pricing (Accessed 22 April 2024).

Zhu, K. et al. Hybrid 2D–CMOS microchips for memristive applications. Nature 618, 57–62 (2023).

4DS Memory. Company update and 2024 imec contract extension. 4DS Memory https://www.aspecthuntley.com.au/asxdata/20231129/pdf/02747367.pdf (2023).

Intrinsic AI Solutions. Intrinsic Semiconductor Technologies secures £7m investment to solve the memory bottleneck for data hungry applications. Intrinsic AI Solutions https://www.intrinsicsemi.com/news/intrinsic-semiconductor-technologies-secures-7m-investment-to-solve-the-memory-bottleneck-for-data-hungry-applications (2023).

Gianfagna, M. Weebit Nano brings ReRAM benefits to the automotive market. Semiwiki https://semiwiki.com/automotive/343154-weebit-nano-brings-reram-benefits-to-the-automotive-market/ (2024).