Decadal plan for semiconductors. Semiconductor Research Corporation https://www.src.org/about/decadal-plan/ (2021).

Generative AI spurs new demand for enterprise SSDs. McKinsey & Company https://www.mckinsey.com/industries/semiconductors/our-insights/generative-ai-spurs-new-demand-for-enterprise-ssds (2024).

Yoon, C.-W. The fundamentals of NAND flash memory: technology for tomorrow’s fourth industrial revolution. IEEE Solid State Circuits Mag. 14, 56–65 (2022).

Mohan, V. et al. Modeling power consumption of NAND flash memories using FlashPower. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 32, 1031–1044 (2013).

LeCun, Y., Bengio, Y. & Hinton, G. Deep learning. Nature 521, 436–444 (2015).

Kim, K. & Park, M. Present and future, challenges of high bandwith memory (HBM). In 2024 IEEE International Memory Workshop (IMW) 1–4 (IEEE, 2024); https://doi.org/10.1109/IMW59701.2024.10536972.

Mehonic, A. & Kenyon, A. J. Brain-inspired computing needs a master plan. Nature 604, 255–260 (2022).

Jones, N. How to stop data centres from gobbling up the world’s electricity. Nature 561, 163–166 (2018).

Tanaka, H. et al. Bit cost scalable technology with punch and plug process for ultra high density flash memory. In 2007 IEEE Symposium on VLSI Technology 14–15 (IEEE, 2007); https://doi.org/10.1109/VLSIT.2007.4339708.

International Roadmap for Devices and Systems. Mass Digital Storage (IEEE, 2023); https://doi.org/10.60627/4hs9-2098.

Dayarathna, M., Wen, Y. & Fan, R. Data center energy consumption modeling: a survey. IEEE Commun. Surv. Tutor. 18, 732–794 (2016).

Kim, S. S. et al. Review of semiconductor flash memory devices for material and process issues. Adv. Mater. 35, 2200659 (2023).

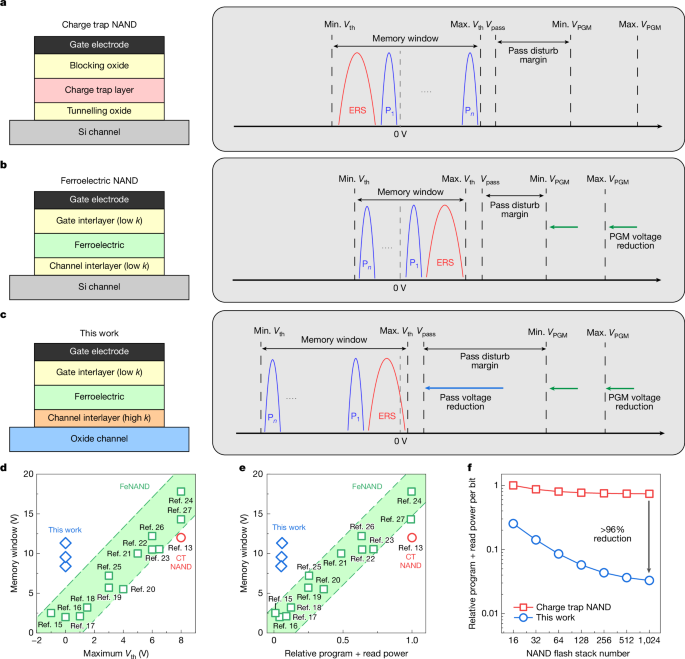

Du, P.-Y. et al. an extremely scaled hemi-cylindrical (HC) 3D NAND device with large Vt memory window (>10V) and excellent 100K endurance. In 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020); https://doi.org/10.1109/VLSITechnology18217.2020.9265078.

Mo, F. et al. Experimental demonstration of ferroelectric HfO2 FET with ultrathin-body IGZO for high-density and low-power memory application. In 2019 Symposium on VLSI Technology T42–T43 (IEEE, 2019); https://doi.org/10.23919/VLSIT.2019.8776553.

Kim, M.-K., Kim, I.-J. & Lee, J.-S. CMOS-compatible ferroelectric NAND flash memory for high-density, low-power, and high-speed three-dimensional memory. Sci. Adv. 7, eabe1341 (2021).

Florent, K. et al. Vertical ferroelectric HfO2 FET based on 3-D NAND architecture: towards dense low-power memory. In 2018 IEEE International Electron Devices Meeting (IEDM) 2.5.1–2.5.4 (IEEE, 2018); https://doi.org/10.1109/IEDM.2018.8614710.

Chen, C.-K. et al. First demonstration of ultra-low Dit top-gated ferroelectric oxide-semiconductor memtransistor with record performance by channel defect self-compensation effect for BEOL-compatible non-volatile logic switch. In 2022 International Electron Devices Meeting (IEDM) 6.1.1–6.1.4 (IEEE, 2022); https://doi.org/10.1109/IEDM45625.2022.10019440.

Ali, T. et al. A multilevel FeFET memory device based on laminated HSO and HZO ferroelectric layers for high-density storage. In 2019 IEEE International Electron Devices Meeting (IEDM) 28.7.1–28.7.4 (IEEE, 2019); https://doi.org/10.1109/IEDM19573.2019.8993642.

Aabrar, K. A. et al. BEOL-compatible superlattice FEFET analog synapse with improved linearity and symmetry of weight update. IEEE Trans. Electron Devices 69, 2094–2100 (2022).

Lim, S. et al. Comprehensive design guidelines of gate stack for QLC and highly reliable ferroelectric VNAND. In 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023); https://doi.org/10.1109/IEDM45741.2023.10413820.

Kim, I.-J. & Lee, J.-S. Unlocking large memory windows and 16-level data per cell memory operations in hafnia-based ferroelectric transistors. Sci. Adv. 10, eadn1345 (2024).

Kim, G. et al. In-depth analysis of the hafnia ferroelectrics as a key enabler for low voltage & QLC 3D VNAND beyond 1K layers: experimental demonstration and modeling. In 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024); https://doi.org/10.1109/VLSITechnologyandCir46783.2024.10631559.

Yoon, S. et al. QLC programmable 3D ferroelectric NAND flash memory by memory window expansion using cell stack engineering. In 2023 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2023); https://doi.org/10.23919/VLSITechnologyandCir57934.2023.10185294.

Yoo, S. et al. Highly enhanced memory window of 17.8V in ferroelectric FET with IGZO channel via introduction of intermediate oxygen-deficient channel and gate interlayer. In 2024 IEEE Symposium on VLSI Technology and Circuits (VLSI Technology and Circuits) 1–2 (IEEE, 2024); https://doi.org/10.1109/VLSITechnologyandCir46783.2024.10631534.

Kim, K. et al. Gate-stack optimization to mitigate the cylindrical effect in ferroelectric VNAND. In 2024 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024); https://doi.org/10.1109/IEDM50854.2024.10873530.

Kuk, S.-H. et al. Superior QLC retention (10 years, 85 °C) and record memory window (12.2 V) by gate stack engineering in ferroelectric FET: from “MIFIS” to”MIKFIS”. In 2024 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024); https://doi.org/10.1109/IEDM50854.2024.10873472.

Joh, H. et al. Oxide channel ferroelectric NAND device with source-tied covering metal structure: wide memory window (14.3 V), reliable retention (> 10 years) and disturbance immunity (ΔVth ≤ 0.1 V) for QLC oOperation. In 2024 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024); https://doi.org/10.1109/IEDM50854.2024.10873376.

Qin, Y. et al. Clarifying the role of ferroelectric in expanding the memory window of ferroelectric FETs with gate-side injection: isolating contributions from polarization and charge trapping. In 2024 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024); https://doi.org/10.1109/IEDM50854.2024.10873569.

Das, D. et al. Experimental demonstration and modeling of a ferroelectric gate stack with a tunnel dielectric insert for NAND applications. In 2023 International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2023); https://doi.org/10.1109/IEDM45741.2023.10413697.

Lee, H. J. et al. Laminated ferroelectric FET with large memory window and high reliability. IEEE Trans. Electron Devices 71, 2411–2416 (2024).

Venkatesan, P. et al. Demonstration of robust retention in band engineered FEFETs for NAND storage applications using tunnel dielectric layer. IEEE Electron Device Lett. 46, 397–400 (2025).

Ichihara, R. et al. Re-examination of Vth window and reliability in HfO2 FeFET based on the direct extraction of spontaneous polarization and trap charge during memory operation. In 2020 IEEE Symposium on VLSI Technology 1–2 (IEEE, 2020); https://doi.org/10.1109/VLSITechnology18217.2020.9265055.

Deng, S. et al. Examination of the interplay between polarization switching and charge trapping in ferroelectric FET. In 2020 IEEE International Electron Devices Meeting (IEDM) 4.4.1–4.4.4 (IEEE, 2020); https://doi.org/10.1109/IEDM13553.2020.9371999.

Kim, I.-J., Kim, M.-K. & Lee, J.-S. Design strategy to improve memory window in ferroelectric transistors with oxide semiconductor channel. IEEE Electron Device Lett. 44, 249–252 (2023).

Yoo, S. et al. An analytical interpretation of the memory window in ferroelectric field-effect transistors. Appl. Phys. Lett. 123, 222902 (2023).

Jiang, Z. et al. On the origin of holes during polarization reset in floating body ferroelectric FETs towards improving switching efficiency. In 2024 IEEE International Electron Devices Meeting (IEDM) 1–4 (IEEE, 2024); https://doi.org/10.1109/IEDM50854.2024.10873452.

Suh, K.-D. et al. A 3.3 V 32 Mb NAND flash memory with incremental step pulse programming scheme. IEEE J. Solid State Circuits 30, 1149–1156 (1995).

Ni, K. et al. Critical role of interlayer in Hf0.5Zr0.5O2 ferroelectric FET nonvolatile memory performance. IEEE Trans. Electron Devices 65, 2461–2469 (2018).

Monzio Compagnoni, C. et al. Reviewing the evolution of the NAND flash technology. Proc. IEEE 105, 1609–1633 (2017).

Cheong, W. et al. A flash memory controller for 15μs ultra-low-latency SSD using high-speed 3D NAND flash with 3μs read time. In 2018 IEEE International Solid-State Circuits Conference – (ISSCC) 338–340 (IEEE, 2018); https://doi.org/10.1109/ISSCC.2018.8310322.

Cai, Y., Luo, Y., Ghose, S. & Mutlu, O. Read disturb errors in MLC NAND flash memory: characterization, mitigation, and recovery. In 2015 45th Annual IEEE/IFIP International Conference on Dependable Systems and Networks 438–449 (IEEE, 2015); https://doi.org/10.1109/DSN.2015.49.

Mulaosmanovic, H., Mikolajick, T. & Slesazeck, S. Accumulative polarization reversal in nanoscale ferroelectric transistors. ACS Appl. Mater. Interfaces 10, 23997–24002 (2018).

Jung, T.-S. et al. A 3.3 V 128 Mb multi-level NAND flash memory for mass storage applications. In 1996 IEEE International Solid-State Circuits Conference. Digest of TEchnical Papers, ISSCC 32–33 (IEEE, 1996); https://doi.org/10.1109/ISSCC.1996.488501.

Kim, B. et al. A high-performance 1Tb 3b/cell 3D-NAND flash with a 194MB/s write throughput on over 300 layers. In 2023 IEEE International Solid-State Circuits Conference (ISSCC) 27–29 (IEEE, 2023); https://doi.org/10.1109/ISSCC42615.2023.10067666.

Resnati, D. et al. Characterization and modeling of temperature effects in 3-D NAND flash arrays—Part I: Polysilicon-induced variability. IEEE Trans. Electron Devices 65, 3199–3206 (2018).

Lee, S.-T. & Lee, J.-H. Review of neuromorphic computing based on NAND flash memory. Nanoscale Horiz. 9, 1475–1492 (2024).

Haque, R. & Mossa, S. F. On-chip charge pump design for 3D non-volatile flash memory: from industry perspective. Integration 94, 102093 (2024).

Jeong, W. et al. A 128 Gb 3b/cell V-NAND flash memory with 1 Gb/s I/O rate. IEEE J. Solid State Circuits 51, 204–212 (2016).

Wong, O. Y., Wong, H., Tam, W. S. & Kok, C. W. A comparative study of charge pumping circuits for flash memory applications. Microelectron. Reliab. 52, 670–687 (2012).

Mossa, S. & Haque, R. Application of negative pump for higher bits/cell in circuit-under array 3D NAND flash memory. Preprint at Authorea https://doi.org/10.22541/au.169822443.30652906/v1 (2023).

Khakifirooz, A. et al. A 1.67Tb, 5b/cell flash memory fabricated in 192-layer floating gate 3D-NAND technology and featuring a 23.3 Gb/mm2 bit density. IEEE Solid State Circuits Lett. 6, 161–164 (2023).

Toprasertpong, K., Takenaka, M.& Takagi, S. Direct observation of interface charge behaviors in FeFET by quasi-static split C-V and Hall techniques: revealing FeFET operation. In 2019 IEEE International Electron Devices Meeting (IEDM) 23.7.1–23.7.4 (IEEE, 2019); https://doi.org/10.1109/IEDM19573.2019.8993664.

Toprasertpong, K., Takenaka, M. & Takagi, S. On the strong coupling of polarization and charge trapping in HfO2/Si-based ferroelectric field-effect transistors: overview of device operation and reliability. Appl. Phys. A 128, 1114 (2022).

Schroeder, U., Park, M. H., Mikolajick, T. & Hwang, C. S. The fundamentals and applications of ferroelectric HfO2. Nat. Rev. Mater. 7, 653–669 (2022).

Hoffmann, M. et al. Fast read-after-write and depolarization fields in high endurance n-type ferroelectric FETs. IEEE Electron Device Lett. 43, 717–720 (2022).

Mativenga, M., Haque, F., Billah, M. M. & Um, J. G. Origin of light instability in amorphous IGZO thin-film transistors and its suppression. Sci. Rep. 11, 14618 (2021).

Frickey, R. et al. Comparing the reliability of solid-state drives based on TLC and QLC NAND flash memories (invited). In 2024 IEEE International Reliability Physics Symposium (IRPS) 3 A.1-1–3 A.1-7 (IEEE, 2024); https://doi.org/10.1109/IRPS48228.2024.10529487.

Hur, J. et al. Characterizing ferroelectric properties of Hf0.5Zr0.5O2 from deep-cryogenic temperature (4 K) to 400 K. IEEE J. Explor. Solid State Comput. Devices Circuits 7, 168–174 (2021).

Zhou, D. et al. Electric field and temperature scaling of polarization reversal in silicon doped hafnium oxide ferroelectric thin films. Acta Mater. 99, 240–246 (2015).