Preparation of the substrate

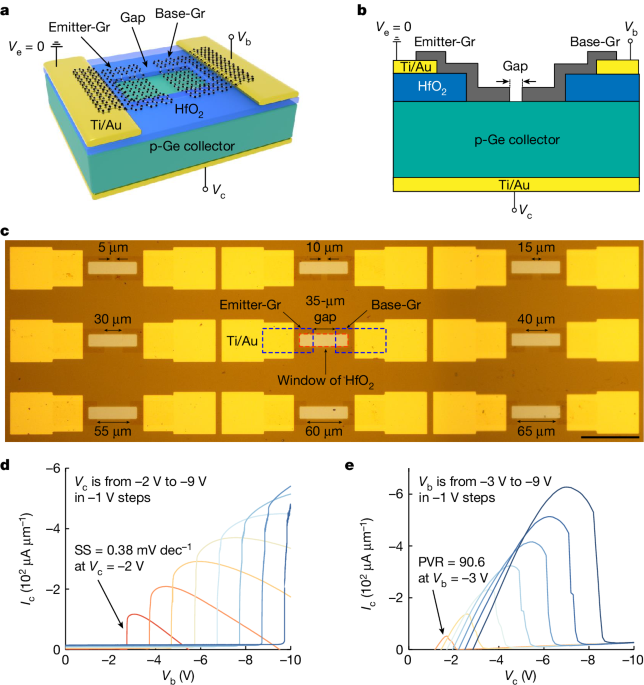

A p-type (100) Ge substrate with a resistivity of 1â10âΩâcm was cleaned by hydrofluoric acid (40âwt%) for 60âs to remove native oxide on the surface. A 30-nm-thick HfO2 insulating layer was deposited on top of the Ge substrate by atomic layer deposition at 200â°C (precursors, tetrakis (dimethylamido) hafnium (Hf (NMe2)4) and water). The bottom of the Ge substrate was scratched, and Ti/Au (5/50ânm) metallization was performed by electron beam evaporation to form an ohmic contact. Electrode metallization using Ti/Au (5/50ânm) on the surface was formed by photolithography and electron beam evaporation. For photolithography, photoresist s-1813 (spin-coated at 3,000ârpm for 30âs, baked at 120â°C for 2âmin) and LOR3A (spin-coated at 3,000ârpm for 50âs, baked at 190â°C for 5âmin) were used in sequence. The HfO2 layer on the substrate was then patterned by photolithography and reactive ion etching (CF4 50âstandard cubic centimetres per minute (sccm), 5.0âPa, radiofrequency power 100âW, 5.5âmin), followed by dilute hydrofluoric acid (5âwt%) etching for 30âs to form a window to the Ge.

Preparation of the monolayer Gr film

Monolayer Gr film was synthesized by chemical vapour deposition on a commercial copper foil (99.9%, 25-μm thick). The copper foil was first annealed at 1,000â°C under a 5-sccm hydrogen flow and then exposed to a mixture of hydrogen (5âsccm) and methane (60âsccm) at a total pressure of 100âPa for 30âmin to grow Gr, followed by slow cooling to room temperature.

Gr film transfer and device fabrication

Gr was transferred by using the typical wet polymethyl methacrylate (PMMA) method. The solution of PMMA (950âkDa molecular weight, Sigma, 4âwt% in ethyl lactate) was first spin-coated on the graphene/Cu foil at 2,000ârpm for 60âs and cured at 180â°C for 15âmin. After removing the Cu foil by chemical etching, the PMMA/Gr film was carefully collected on the desired target substrate and baked. PMMA was then removed by immersing in acetone at 50â°C to complete the transfer. Finally, the transferred Gr was patterned by photolithography and oxygen plasma etching (200âW, 180âsccm, 2âmin).

The emission process in the SEHC mechanism

When the collector current increases abruptly, (A) the electric field in the emitter-Gr heats the holes there while (B) high-energy holes are injected from Ge into the base-Gr, which will arrive at the emitter-Gr by (C) diffusion. Only one injected hole is shown (Extended Data Fig. 6a). The arrived high-energy holes will pass their energy to the heated ones through (D1) CCS32 (Extended Data Fig. 6b). When the stimulated holes in the emitter-Gr gain enough energy from the injected holes, (D2) a multiplication process happens (Extended Data Fig. 6c), before the stimulated holes with enough energy are (D3) emitted into Ge with the reverse bias there, leading to the abrupt current (Extended Data Fig. 6d).

In the CCS process, after one collision between carriers, the number of carriers that can cross the Gr/Ge barrier will double, and the energy these carriers possess after the collision is still higher than the Gr/Ge barrier. In addition, the lateral electric field generated by Vb can increase these carriersâ energy. Therefore, the carriers after the collision can continue to participate in the CCS, causing the number of carriers that can cross the barrier to double again. Meanwhile, In the energy domain, the CCS will result in a high-energy-band tail in the energy distribution function, indicating an increase in high-energy carrier distribution32. Therefore, the continuous CCS process can cause the number of high-energy carriers in the emitter-Gr to increase repeatedly, leading to a surge in the reverse current. It should be noted that the impact ionization47 cannot be responsible for this phenomenon, as that Ic never increases abruptly no matter how large Vb and the corresponding electric field is applied (before the device is damaged) in the emitter-Gr if the base-Gr/Ge junction is not forward biased.

Modelling of the CCS multiplication process

The base bias Vb determines the current Ic not only by providing a lateral electric field in the emitter-Gr but also by controlling the injected carriers at the base-Gr/Ge junction, leading to a complex relationship among the scattering, the multiplication and Vb, and therefore a complex one between Ic and Vb. In fact, multiplication processes are usually modelled using an experience-based approach47 and we provide an empirical model for the multiplication process in the HOET below.

The critical base bias Vb-critical, where Ic increases abruptly, increases linearly with the collector bias Vc (Fig. 2e) and the gap length dgap (Fig. 2f). On the basis of these experimental results, Ic is described as Icâ=âMâÃâIrevâ+âI0, Mâ=âA/(1âââ(VbâââVc)/(Vb-criticalâââVc)), Vb-criticalâ=âBdgapâ+âVcâ+âC, where Irev is the reverse current of the emitter-Gr/Ge junction before the CCS multiplication, M is the CCS multiplication factor and I0, A, B and C are fitting constants. As shown in Extended Data Fig. 6e, the model fits the experimental results well.

Modelling of the Gr/Ge junction

On the basis of the thermionic-emission current model of a Schottky junction, the Gr/p-Ge Schottky potential barrier height qÏB, ideality factor η, interface state density Dit and series resistance Rs are estimated as follows. The relationship of the forward current IF of the Gr/Ge junction and temperature T is ln(IF/T2)â=âCâââq(ÏBâââVc/η)/kâÃâ(1/T), where C is a constant, q is the elementary charge, Vc is the forward voltage bias and k is Boltzmannâs constant3. Using an Arrhenius plot, the slopes of the fitted lines âq(ÏBâââVc/η)/1,000k is plotted against Vc (Extended Data Fig. 3c), and the y intercept at 0âV is S0â=ââqÏB/1,000k leading to a qÏB of about 0.38âeV, while the slope is Slope*â=âq/1,000kη leading to an η of about 1.29. Dit is estimated using η and ÏB based on a relationship of ηâ=â1â+â(δ/ε0)(εs/Wdâ+âq2Dit), where δ is the thickness of an interfacial layer between Gr and Ge, ε0 is the permittivity in vacuum (8.85âÃâ10â14âFâcmâ1), εs is the relative dielectric constant (16.2) of Ge and Wd is the thickness of the depletion layer of Ge (ref. 3). Wdâ=â(2εs/qNaâÃâ(ÏbiâââVcâââkT/q))0.5 where Na is the doping concentration of Ge (1016âcmâ3) and Ïbi is the built-in potential barrier height in the semiconductor as Ïbiâ=âÏBâââÏn. Ïnâ=âkT/qâÃâln(Nv/Na) where Nv is the effective states density of the valence band of Ge (5.7âÃâ1018âcmâ3). On the basis of these models, Dit is estimated to be about 2.6âÃâ1012âcmâ2âeVâ1. A series resistance Rs of the junction of about 3âkΩ is extracted by a linear fitting of the forward IâV characteristic at a high voltage bias (Extended Data Fig. 3d).

Characterization

Characterization of the graphene film and the devices was performed using a confocal Raman spectrometer (Jobin Yvon Lab RAM HR800), an optical microscope (Nikon LV100ND), a scanning electron microscope (FEI XL30 SFEG using an accelerating voltage of 10âkV) and an atomic force microscope (Bruker Dimension Icon AFM). The transistors were measured using a semiconductor analyser (Agilent B1500A with a capacitance measurement unit B1500A-A20) and a probe station (Cascade Microtech 150-PK-PROMOTION) at room temperature, and a vacuum probe station (Lake Shore TTPX/TSM1D1001) at low temperature.

For device uniformity, taking the device with a 3-μm gap as an example, 20 devices were fabricated on a wafer. The transfer characteristics (Vcâ=ââ2âV) show that for SS, sample sizeâ=â20, meanâ=â0.60âmVâdecâ1 and standard deviation =â0.29âmVâdecâ1, whereas the output characteristics (Vbâ=ââ4âV) show that for PVR, sample sizeâ=â20, meanâ=â15.80 and standard deviation =â2.84. The uniformity can be improved by advanced processes, such as using a Gr-on-Ge wafer where the Gr is grown directly on Ge instead of manual Gr transfer48.

Opportunities and challenges

The SEHC mechanism can be applied to devices composed of different materials. For example, using a carbon nanotube film/n-Ge junction, n-type HOETs can be fabricated (Extended Data Fig. 10). Complex circuits can be realized by using both the n-type and p-type HOETs. However, for the HOET to ultimately become practical, a series of problems must be solved including increasing the range of the current with an SS less than 60âmVâdecâ1, improving the PVR in the NDR applications and reducing the hysteresis in the characteristics.

At present, although the on-current of the transistor is high, the off-current is also high, resulting in a limited current range with a SS less than 60âmVâdecâ1, which is not an intrinsic result of the SEHC mechanism. The off-current should be reduced and the on-current increased to improve the on-to-off current ratio. To reduce the off-current, (1) the quality of the Gr/semiconductor interface should be improved by using a Gr-on-Ge wafer where the Gr is grown directly on Ge instead of being transferred48 and (2) other material combinations can be used, such as Gr combined with wider-bandgap semiconductors, where the potential barrier height of the Gr/semiconductor junction is higher and the intrinsic carrier concentration in the semiconductor is lower. To increase the on-current, the energy of the carriers injected from the base-Gr should be further increased, perhaps by using asymmetric potential barriers of the base/substrate and emitter/substrate junctions, which can be achieved by using different substrate semiconductor materials under the base-Gr and the emitter-Gr. These requirements are also necessary for improving the PVR in the NDR applications.

Typical transfer and output characteristics show that the width of the hysteresis window is about 0.25âV and 0.23âV, respectively. However, it should be noted that the hysteresis is not caused by the SEHC mechanism intrinsically, but by the limited quality of the Gr/Ge interface. Because of the contamination and imperfection during the transfer and fabrication process, the Gr/Ge junction itself shows a large hysteresis. This can be reduced by using a Gr-on-Ge wafer where the Gr is grown directly on Ge instead of being transferred or by using an encapsulation.